产品中心

NVME Host IP Core

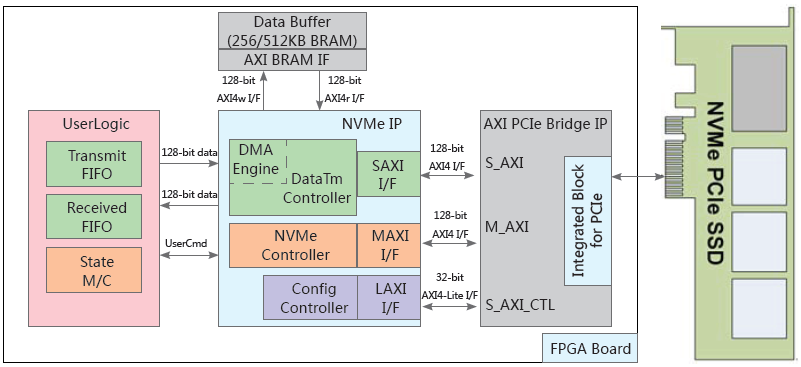

NVMe Host IP Core 用于实现基于FPGA 或ASIC 的主机控制器高速读写访问NVMe PCIe SSD,符合NVM express 标准。该IP 采用Xilinx 的AXI PCIeBridge IP 作为PCIe 协议传输,通过访问PCIe 和NVMe 控制器寄存器来实现NVMe 协议命令,即识别,写和读命令等。通常,PCIE NVMe SSD 包括多个SSD 控制器,因此从每个SSD 返回的数据请求可能不是顺序格式,需要由BRAM 实现的大数据缓冲器来支持来自SSD 的随机数据请求。该IP 核提供两种缓冲区大小的NVMe IP 运行配置,模式1 中的IP 是使用256K 字节缓冲器的经济模式。模式2 中的IP 是使用512 K 字节缓冲区的高性能模式。简单的dgIF typeS 用户接口,只需命令,起始地址和传输长度用于命令接口和通用FIFO 用于数据接口。由于IP 中没有异步逻辑,IP 的时钟域必须使用与AXI PCIeBridge IP 的输出相同的时钟。如果IP 在数据包传输期间检测到异常情况,则错误信号将被确认为错误状态。

NVMe IP Core 运行在带有AXI PCIeBridge IP 的基础上,旨在无CPU 或DDR 参与下访问NVMe PCIe SSD。基于BlockRAM 实现的256KB 或512 KB 缓冲区用于在用户逻辑和PCIe SSD 之间传输数据。该NVMe IP Core 可典型应用于基于FPGA 和ASIC 的高带宽吞吐性能以及大容量存储设备设计,也可以应用于对体积要求敏感的嵌入式小尺寸存储设备设计。可控制访问PCIE 规格的NVME SSD,U2 规格的NVME SSD,M2 规格的NVME SSD 等。

- 产品特点

- 技术规格

- 订货信息

- 资料下载

• 实现应用层直接访问NVMe PCIe SSD,无需CPU 介入操作

• 持续读性能高达2.5GB/s,持续写性能高达1.5GB/s

• 简单的dgIF typeS 用户接口

• PCIe IP 通过使用128 位总线接口直接连接到Xilinx 的AXI 总线

• 通过128 位AXI4 总线接口连接256 KB(MODE = 1)或512 KB(MODE = 2)数据缓冲器(通过使用DDR 可支持更大的缓冲区大小)

• 支持IDENTIFY,WRITE 和READ 命令

• 支持标准的NVMe 存储设备

• 基类代码:01h(大容量存储),子类代码:08h(非易失性),编程接口:02h(NVMHCI)

• MPSMIN(最小内存页大小):0(4Kbyte)

• MDTS(最大数据传输大小):0(无限制)或至少5(128 K 字节)

• 持续读性能高达2.5GB/s,持续写性能高达1.5GB/s

• 简单的dgIF typeS 用户接口

• PCIe IP 通过使用128 位总线接口直接连接到Xilinx 的AXI 总线

• 通过128 位AXI4 总线接口连接256 KB(MODE = 1)或512 KB(MODE = 2)数据缓冲器(通过使用DDR 可支持更大的缓冲区大小)

• 支持IDENTIFY,WRITE 和READ 命令

• 支持标准的NVMe 存储设备

• 基类代码:01h(大容量存储),子类代码:08h(非易失性),编程接口:02h(NVMHCI)

• MPSMIN(最小内存页大小):0(4Kbyte)

• MDTS(最大数据传输大小):0(无限制)或至少5(128 K 字节)

- NVME Host IP Core 产品简介.pdf[ 642KB ]