产品中心

SATAIII HOST IP Core

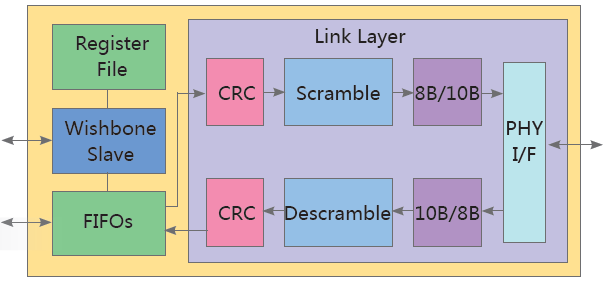

SATA 主控制器 IP 核为大容量存储设备的SATAIII 连接提供了高速串口链路接口。串行链路高速差分层是利用千兆技术和8b/10b编码技术。

串行ATA 链路层和传输层核心实现了SATA 主机接口,通过10/20/40 位接口连接到SATA PHY,WISHBONE从接口用于寄存器和DMA访问。主要包括具有到物理层的10/20/40位数据路径的链路层模块和通过WISHBONE 从接口连接到系统的传输层模块。

SAPIS PHY 接口

此接口可连接到任何SAPIS 兼容串行ATA PHY。包括电源管理和速度协商信号。PHY 接口与PHY 时钟域同步,PHY 时钟域可以具有与系统时钟域不同的时钟频率。同步由串行ATA 链路和传输层核心完成。

DMA 连接

提供简单的握手信号从而将DMA 单元连接到核心模块。一旦任何发送数据可用或者在内核的数据FIFO 中需要读取,DMA 请求将被置位。然后DMA 单元将通过WISHBONE 从设备接口访问数据FIFO。系统中断将在数据传输完成时通知主机软件。

自动流控制机制控制数据调节,以避免发送数据FIFO 的下溢或上溢。可以调整数据FIFO 阈值以优化数据流控制。DMA 单元(或主机软件)可以以任何速度工作,无数据丢失的风险。

- 产品特点

- 技术规格

- 订货信息

- 资料下载

• 低延时:读IOPS 66K@4k,写IOPS 67K@4k

• 异步,不受SoC 时钟限制,独立于PHY 时钟

• 基于Xilinx 收发器的PHY

• 符合SATA3.0 规范:支持NCQ,基于FIS 的交换

• 支持1.5Gbps,3.0Gbps 和6.0Gbps

• AXI Light 接口用于寄存器访问

• AXI 流接口用于数据传输

• 支持PIO,DMA 和FPDMA 传输

• 实现寄存器块和串行ATA 状态和控制寄存器

• 支持48 位地址功能集

• 支持电源管理

• 支持DMA

• 基于描述符的命令处理

• 命令列表大小无限制

• 支持多种配置选项

• ucLinux 驱动程序

• 低延时:读IOPS 66K@4k,写IOPS 67K@4k

• 异步,不受SoC 时钟限制,独立于PHY 时钟

• 基于Xilinx 收发器的PHY

• 符合SATA3.0 规范:支持NCQ,基于FIS 的交换

• 支持1.5Gbps,3.0Gbps 和6.0Gbps

• AXI Light 接口用于寄存器访问

• AXI 流接口用于数据传输

• 支持PIO,DMA 和FPDMA 传输

• 实现寄存器块和串行ATA 状态和控制寄存器

• 支持48 位地址功能集

• 支持电源管理

• 支持DMA

• 基于描述符的命令处理

• 命令列表大小无限制

• 支持多种配置选项

• ucLinux 驱动程序

- SATA HOST IP Core 产品简介.pdf[ 226KB ]