产品中心

SATAII Device IP Core

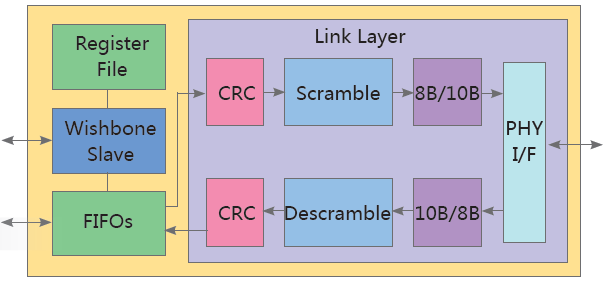

SATA 设备控制器IP 核为大容量存储设备的SATA 连接提供了高速串口链路接口。串行链路高速差分层是利用千兆技术和8b/10b编码技术。

串行ATA 链路层和传输层核心实现了SATA 设备端接口,通过10 位接口连接到SATA PHY,并提供用于寄存器和DMA 访问的WISHBONE从设接口。它由链路层模块以及通过WISHBONE 从接口连接到系统的传输层模块组成。

SAPIS PHY 接口

SAPIS PHY 接口可连接到任何SAPIS 兼容串行ATA PHY。包括电源管理和速度协商信号。PHY 接口与PHY 时钟域同步,PHY 时钟域可以具有与系统时钟域不同的时钟频率。同步由串行ATA 链路和传输层核心完成。

WISHBONE 从接口

WISHBONE 从接口用于访问所有内核的内部寄存器以及数据FIFO。软件或外部DMA 单元可将发送数据写入数据FIFO 或从FIFO 读取。

DMA 连接

提供简单的握手信号从而将DMA 单元连接到核心模块。一旦任何发送数据可用或者在内核的数据FIFO 中需要读取,DMA 请求将被置位。然后DMA 单元将通过WISHBONE 从设备接口访问数据FIFO。系统中断将在数据传输完成时通知设备软件。自动流控制机制控制数据调节,以避免发送数据FIFO 的下溢或上溢。可以调整数据FIFO 阈值以优化数据流控制。DMA 单元(或设备软件)可以以任何速度工作,无数据丢失的风险。

- 产品特点

- 技术规格

- 订货信息

- 资料下载

• 连接符合SAPIS 的SATA PHY

• 符合SATA Gen 1(1.5 Gb/s)和Gen 2(3.0Gb/s)

• Wishbone 从设备接口用于寄存器访问和FIFO/DMA 数据传输

• 只有非常少的FF 在PHY 时钟域,主要部分在Wishbone 时钟

• 128 字节(32 双字) 数据FIFO( 可选256 字节)

• 实现任务文件,非标准SATA 状态和控制寄存器,特定器件寄存器和本机模式寄存器

• 中断和DMA 握手(外部DMA)

• 支持48 位地址功能集

• 8b/10b 编码和解码

• CONT 和数据加扰器以减少EMI

• CRC 生成和检查

• 自动插入HOLD 原语

• 支持电源管理

• 可选的本机模式编程模型

• 支持多配置选项

• 10 位PHY 接口

• 连接符合SAPIS 的SATA PHY

• 符合SATA Gen 1(1.5 Gb/s)和Gen 2(3.0Gb/s)

• Wishbone 从设备接口用于寄存器访问和FIFO/DMA 数据传输

• 只有非常少的FF 在PHY 时钟域,主要部分在Wishbone 时钟

• 128 字节(32 双字) 数据FIFO( 可选256 字节)

• 实现任务文件,非标准SATA 状态和控制寄存器,特定器件寄存器和本机模式寄存器

• 中断和DMA 握手(外部DMA)

• 支持48 位地址功能集

• 8b/10b 编码和解码

• CONT 和数据加扰器以减少EMI

• CRC 生成和检查

• 自动插入HOLD 原语

• 支持电源管理

• 可选的本机模式编程模型

• 支持多配置选项

- SATA Device IP Core 产品简介.pdf[ 226KB ]